M.P.J. Tiggelman

# Thin Film Barium Strontium Titanate Capacitors for Tunable RF Front-end Applications

M.P.J. Tiggelman

## THIN FILM BARIUM STRONTIUM TITANATE CAPACITORS FOR TUNABLE RF FRONT-END APPLICATIONS

Markus Petrus Josephus Tiggelman

#### Samenstelling promotiecommissie:

Voorzitter: prof.dr.ir. A.J. Mouthaan Universiteit Twente Secretaris: prof.dr.ir. A.J. Mouthaan Universiteit Twente Promotor: Universiteit Twente prof.dr. J. Schmitz Ass. Promotor: Universiteit Twente dr.ir. R.J.E. Hueting Referent: dr. K. Reimann NXP Semiconductors Leden: prof.dr.ing. D.H.A. Blank Universiteit Twente prof.dr.ir. B. Nauta Universiteit Twente

prof.dr.ir. B. Nauta Universiteit Twente

prof.dr.ir. R.A.M. Wolters Universiteit Twente,

NXP Semiconductors

adj.prof.dr.ir. R. Jos Universiteit Chalmers, NXP Semiconductors

Ph.D. dissertation: University of Twente, The Netherlands.

Title: THIN FILM BARIUM STRONTIUM TITANATE

CAPACITORS FOR TUNABLE RF FRONT-END

APPLICATIONS

Author: M.P.J. Tiggelman ISBN: 978-90-365-2937-2

Printing: Printservice Technical University of Eindhoven.

This research was funded by NXP Semiconductors in cooperation with Philips Research Laboratories and the University of Twente. Partial support came from the European IST project NANOSTAR.

©M.P.J. Tiggelman 2009. All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

## THIN FILM BARIUM STRONTIUM TITANATE CAPACITORS FOR TUNABLE RF FRONT-END APPLICATIONS

#### PROEFSCHRIFT

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof.dr. H. Brinksma,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op donderdag 3 december 2009 om 16:45 uur

door

Markus Petrus Josephus Tiggelman geboren op 4 oktober 1977 te Enschede

#### Dit proefschrift is goedgekeurd door:

de promotor: prof.dr. J. Schmitz de ass. promotor: dr.ir. R.J.E. Hueting

### Contents

| 1        | Intr | oducti  | ion 1                                   | L |

|----------|------|---------|-----------------------------------------|---|

|          | 1.1  | Scope   |                                         | 1 |

|          | 1.2  | Outlin  | ıe 5                                    | 5 |

| <b>2</b> | Tur  | able to | echnologies in RF applications 7        | 7 |

|          | 2.1  | Introd  | uction                                  | 7 |

|          | 2.2  | Techn   | ologies                                 | 3 |

|          |      | 2.2.1   | Varicaps                                | ) |

|          |      | 2.2.2   | Dielectric varactors                    | 1 |

|          |      | 2.2.3   | Semiconductor-switched capacitors       | 3 |

|          |      | 2.2.4   | RF-MEMS                                 | L |

|          | 2.3  | Discus  | ssion                                   | 5 |

|          | 2.4  | Conclu  | usions                                  | 3 |

|          | 2.5  | Focus   | on dielectric varactors                 | ) |

| 3        | Fer  | roelect | ric materials and properties 31         | L |

|          | 3.1  | Introd  | uction                                  | L |

|          | 3.2  | Bariur  | m strontium titanate as a ferroelectric | 3 |

|          | 3.3  | Figure  | es of merit                             | 7 |

| 4        | Mea  | asuren  | nent methodology 39                     | ) |

|          | 4.1  | Introd  | uction                                  | ) |

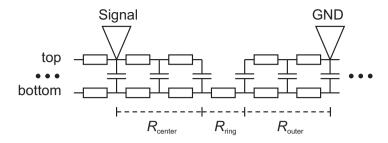

|          | 4.2  | Top-pa  | atterned capacitor test structures      | ) |

|          |      | 4.2.1   | Test structure description              | ) |

|          |      | 4.2.2   | The equivalent capacitor model 41       | L |

|          |      | 4.2.3   | Parasitic capacitances                  | 2 |

|          |      | 4.2.4   | Parasitic resistances                   | 3 |

|          |      | 405     |                                         | 7 |

|          |      | 4.2.5   | Loss tangent separation technique 47    | ſ |

|   | 4.3 | Low fr  | equency r      | measurement methodology                            | . 53 |

|---|-----|---------|----------------|----------------------------------------------------|------|

|   |     | 4.3.1   | Frequenc       | cy and voltage sweeps                              | . 54 |

|   |     | 4.3.2   | Tempera        | ature sweeps                                       | . 55 |

|   | 4.4 | High f  | requency       | Vector Network Analyzer methodology                | . 56 |

|   | 4.5 | _       |                | conclusions                                        |      |

| 5 | Wie | de-band | d bias-te      | es for capacitor characterization                  | 61   |

|   | 5.1 |         |                |                                                    | . 61 |

|   | 5.2 |         |                | owledge on bias-tees                               |      |

|   | 5.3 |         |                | s-tees                                             |      |

|   | 5.4 |         |                | pelectric capacitor characterization               |      |

|   |     | 5.4.1   | Reducing       | g voltage dependence by calibration                | . 64 |

|   |     | 5.4.2   |                | m made bias-tee                                    |      |

|   | 5.5 | Discus  |                | conclusions                                        |      |

| 6 | Fer | roelect | ric capac      | citor characterization and optimization            | 73   |

|   | 6.1 |         |                |                                                    | . 73 |

|   | 6.2 |         |                | rials                                              |      |

|   |     | 6.2.1   |                | e                                                  |      |

|   |     | 6.2.2   | Metal ele      | ectrodes                                           | . 75 |

|   |     | 6.2.3   | Barium s       | strontium titanate                                 | . 76 |

|   | 6.3 | Sample  | e fabricat     | ion                                                | . 77 |

|   |     | 6.3.1   | Alumina        | substrate                                          | . 77 |

|   |     | 6.3.2   | Silicon s      | ubstrate                                           | . 78 |

|   | 6.4 | Micros  | structural     | characterization                                   | . 78 |

|   |     | 6.4.1   |                | substrate                                          |      |

|   |     | 6.4.2   |                | ubstrate                                           |      |

|   | 6.5 |         |                | cterization                                        | . 80 |

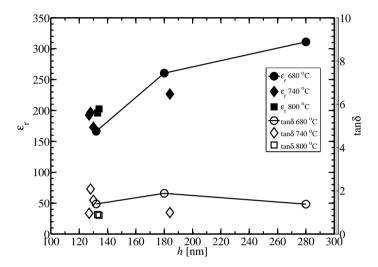

|   |     | 6.5.1   |                | ence of the relative permittivity on processing as | . 81 |

|   |     | 6.5.2   | Electrica      | al properties versus ambient temperature           | . 82 |

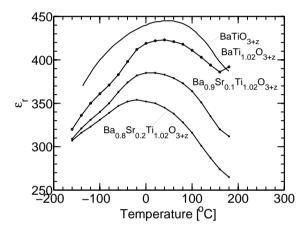

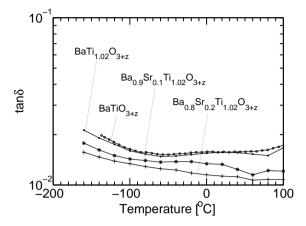

|   |     |         | 6.5.2.1        | Alumina substrate                                  | . 83 |

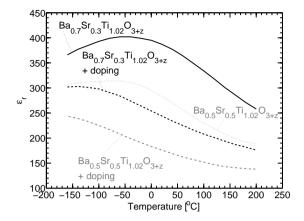

|   |     |         | 6.5.2.2        | Silicon substrate                                  | . 85 |

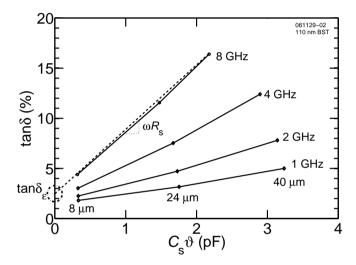

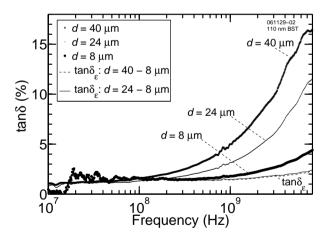

|   |     | 6.5.3   | Small-sig      | gnal properties versus frequency                   | . 86 |

|   |     |         | 6.5.3.1        | Alumina substrate                                  | . 86 |

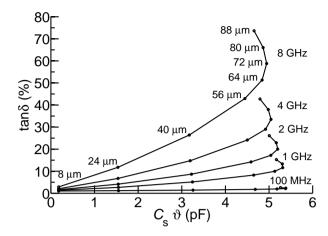

|   |     |         | 6.5.3.2        | Silicon substrate                                  | . 89 |

|   |     | 6.5.4   | $Q$ and $\eta$ | versus electric field                              | . 90 |

|   |     |         | 6.5.4.1        | Alumina substrate                                  | . 90 |

|   |     |         | 6.5.4.2        | Silicon substrate                                  | . 92 |

|   | 6.6 | Discus  | sion           |                                                    | . 96 |

|   | 6.7 | Conclu  | ısions         |                                                    | 101  |

#### CONTENTS

| 7  | Mo                     | del of               | a ferroelectric capacitor in a circuit simulator          | 103        |  |  |

|----|------------------------|----------------------|-----------------------------------------------------------|------------|--|--|

|    | 7.1                    | Introd               | luction                                                   | 103        |  |  |

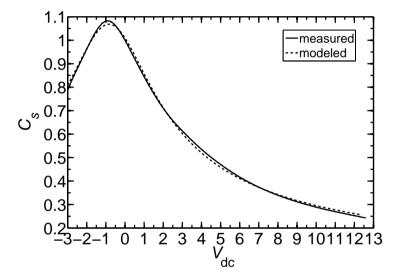

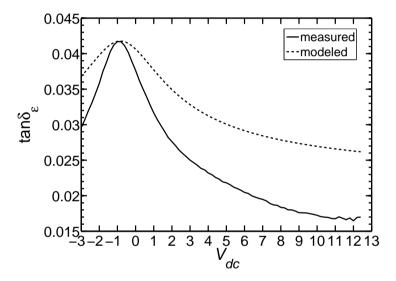

|    | 7.2                    | Model                | description of $C_{\rm s}(V_{\rm dc})$                    | 104        |  |  |

|    | 7.3                    | Model                | description of the losses                                 | 105        |  |  |

|    | 7.4                    | Model                | implementation in ADS                                     | 106        |  |  |

|    | 7.5                    | Discus               | ssion and conclusions                                     | 108        |  |  |

| 8  |                        | olication<br>on stud | on of tunable capacitors in RF circuits - ${f A}$ sindy   | nu-<br>111 |  |  |

|    | 8.1                    | 8.1 Introduction     |                                                           |            |  |  |

|    | 8.2                    | Transı               | mit bandpass filter                                       | 112        |  |  |

|    |                        | 8.2.1                | Relation between the insertion loss and filter parameters | ters115    |  |  |

|    |                        | 8.2.2                | Capacitive or inductive coupling                          | 117        |  |  |

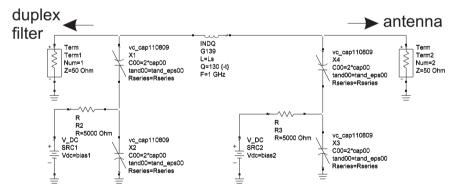

|    |                        | 8.2.3                | Filter implementation in ADS                              | 118        |  |  |

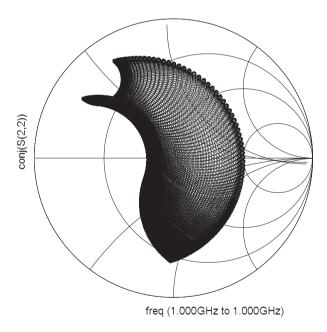

|    | 8.3                    | Imped                | lance matching networks                                   | 120        |  |  |

|    |                        | 8.3.1                | Definitions of Terms                                      | 121        |  |  |

|    |                        | 8.3.2                | Functional requirements and practical consideration       | ıs . 122   |  |  |

|    |                        | 8.3.3                | Impedance matching networks topologies $\dots$ .          | 123        |  |  |

|    |                        | 8.3.4                | Impedance matching network implementations $$             | 125        |  |  |

|    | 8.4                    | Conclu               | usions                                                    | 128        |  |  |

| 9  | Cor                    | clusio               | ns                                                        | 131        |  |  |

| Bi | bliog                  | graphy               |                                                           | 133        |  |  |

| Su | ımm                    | ary                  |                                                           | 153        |  |  |

| Sa | men                    | vatting              | y<br>S                                                    | 155        |  |  |

| Li | List of publications 1 |                      |                                                           |            |  |  |

| Da | ankw                   | oord                 |                                                           | 160        |  |  |

| Bi | ogra                   | phy                  |                                                           | 163        |  |  |

#### Chapter 1

#### Introduction

Mobile phone technology, and more in general wireless technology, demands every year, cheaper and more compact electronic circuitry with more extended functionality. By developing innovative electronic components and by designing state of the art system solutions this request can be fulfilled. In this dissertation we discuss a component for wireless communication, which is used to electrically tune the radio frequency. The tuning of the resonance frequency can be compared by mechanically turning the knob of a classic radio to tune in on a different radio channel.

The radio spectrum, including radio frequencies (RF), covers the frequencies between  $3\,\mathrm{MHz}-30\,\mathrm{GHz}$  [1]. An RF signal is an alternating electrical signal, which can propagate through dielectrics like air and SiO<sub>2</sub>. Applications like, a mobile phone transmits and receives RF signals containing speech or text data.

A mobile phone nowadays can operate at 4 dissimilar (quad-band) radio frequency bands around 850 MHz, 900 MHz, 1800 MHz, and 1900 MHz [2]. The band of operation depends in which part of the world the user operates his or her cellphone.

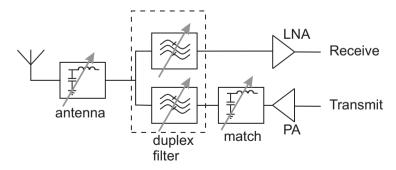

One of the most important hardware parts in a mobile phone is the RF front-end [3], which consists of a number of electronic circuits.

A single-band RF front-end exists of at least a power amplifier (PA), a lownoise amplifier (LNA), a transmit and a receive (duplex) filter, an antenna, and an impedance matching network [3]. The PA amplifies the outgoing signal up to a few watts of power in mobile phones. The LNA amplifies the incoming signal for further processing.

A duplex bandpass filter contains a receive and a transmit band. This bandpass filter strongly suppresses out-of-band signals and only in a limited frequency band a signal can be either transmitted or received, without too much attenuation. The antenna receives and transmits the RF signals.

The purpose of an impedance matching network is to have an optimal power flow from the source to the load to avoid reflections. Preferably the load of the impedance matching network has to absorb all of the power transmitted from the source. To achieve this the source impedance should be equal to the load impedance. A single band RF front-end is realized without any tunable components.

As stated before, modern versatile cellular phones support a large number of standards and frequency bands [2]. For *multi-band* operation multiple non-tunable circuits can be selected by employing multiple switches. Some of these fixed circuits can be replaced by a single tunable circuit to save precious space and components on a printed circuit board.

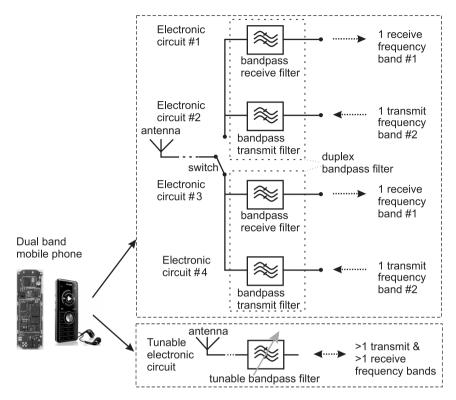

Reconfigurable circuits can tune in on multiple frequencies and can support different standards. A simplified example is given for a dual-band cellphone containing a bandpass filter building block in an RF front-end (see Figure 1.1). A dualband cellphone has two bandpass receive filters, which are set to two different receive frequency bands. Likewise for the transmit bandpass filters. The architecture can consist of 4 separate non-tunable bandpass filter circuits, or 1 tunable bandpass filter which is able to tune in the receive or transmit frequency band of interest, as depicted in Figure 1.1. Tunable components can decrease the dimensions of electronic circuits by exploiting the circuits' reconfigurability.

Most passive tunable technologies are still in the research and development phase and are being optimized for radio frequency (RF) architectures, especially focused on the RF front-end (see Figure 1.2).

The PA and LNA of a multi-band tunable RF front-end both contain active non-tunable components. The three remaining building blocks can be designed with solely passive (tunable) components.

The impedance of the antenna is susceptible to environmental changes in the band of operation [4], e.g., bringing a cellphone to your ear changes the reactive part of the antenna impedance. If the antenna impedance is not corrected for the new load impedance, then the PA will deliver a higher

Figure 1.1 – A simplified example of two design options for a dual-band transmit and receive filter in a mobile phone that supports 4 frequency bands: 1) a design containing 4 separate electronic circuits which support each a single frequency band in which the phone can either receive or transmit signals, or 2) a design containing a single electronic tunable circuit, which supports 4 or more frequency bands.

Figure 1.2 – A completely reconfigurable RF front-end.

transmit power than preferred due to the impedance mismatch and the battery will be drained faster. Optimum receive and transmit energy transfer is obtained, with the LNA and PA, through well-designed tunable impedance matching networks.

The matching networks, duplex filter and antenna are ordinarily designed with passive components, such as resistors, coils and capacitors. Tunable resistors [5] and inductors [6] can be used in these applications. However, electrically tunable components in reconfigurable low-voltage RF circuits are typically metal-insulator-metal (MIM) tunable capacitors for many reasons, especially size, cost, and losses [7].

The main work of this thesis is dedicated to thin film ferroelectric MIM capacitors. These devices are also called dielectric varactors or tunable capacitors. The dielectric layer in these capacitors are made of ferroelectric material.

The advantages of implementing the technology of these devices are a low cost, passive integration on cost-effective substrates, the relatively high permittivity of thin ferroelectric films (typically  $\varepsilon_{\rm r}=100$ –1000), and hence its miniaturization potential due to its high capacitance density, continuous (low voltage) tuning (typically < 40  $\rm V_{dc}$ ), integrated decoupling [8], no hermetic packaging, and no moving parts like in MEMS.

#### 1.1 Scope

The first and foremost topic of this work was to study the potential of (low-cost) thin film ferroelectric capacitors for passive reconfigurable RF front-end applications, e.g., matching networks and filters, within a company research and development project. The objectives were to characterize these capacitors at low and high frequencies, give input to further improve the capacitors RF performance, model the measured tuning of a ferroelectric capacitor, and simulate and design test circuits for RF front-end applications. The simulations should give insight on the feasibility of using dielectric varactors in the test circuits.

The research in this work was performed under industrial boundary conditions at the former Philips [9] Semiconductors Research Laboratories and later NXP Semiconductors Corporate Innovation & Technology [10].

#### 1.2 Outline

This thesis starts with a literature study on relevant tunable capacitor technologies in Chapter 2. The trade-off between the quality factor and tuning ratio of tunable capacitors at microwave frequencies has been assessed in terms of basic physics-based models. In Chapter 3, the focus is put on dielectric varactor technology. A brief introduction is given on the basic properties of ferroelectrics with the emphasis on thin film barium strontium titanate. In Chapter 4, the measurement methodology is elucidated and parasitic capacitances and resistances have been discussed. Additionally, an RF measurement technique is elaborated, which can separate the dielectric loss from the resistive electrode loss, indicate process-induced damage and can show the presence of loss-dominating distributed effects. In Chapter 5 work is presented on how to eliminate voltage-dependent AC impedance measurement errors attributed to a wide-band commercial bias-tee by a measurement technique or by using a voltage-independent in-house bias-tee.

In Chapter 6, the potential of barium strontium titanate MIM capacitors is assessed by characterization on alumina and silicon substrates. In Chapter 7, a model of a ferroelectric capacitor is presented which is implemented in a circuit simulator. In Chapter 8, the design of a narrow-band filter and matching networks are discussed. This thesis ends with the conclusions in Chapter 9.

#### Chapter 2

## Tunable technologies in RF applications

#### 2.1 Introduction

In this Chapter, contemporary tunable capacitor technologies are compared to show their potential for reconfigurable cellular applications [11].

A benchmark of tunable and switchable devices at microwave frequencies is presented on the basis of physical limitations. Performance limitations are outlined for each given technology focusing on the quality factor (Q) and capacitive tuning, i.e., tuning ratio  $(\eta)$ , as figures of merit, which are defined in Section 3.3. If the performance criteria for the Q and  $\eta$  are not met, the application will not be feasible.

The state of the art in terms of quality factor and tuning ratio of several tunable and switchable technologies is visualized and discussed. Topics such as linearity, power handling and temperature stability are important, but could not be handled on such a general base yet and still require a case by case study.

The following technologies play an important role because of their miniaturization and low-power potential: varactor diodes (varicaps), dielectric varactors, integrated transistor-switched capacitors (CMOS<sup>1</sup>, pHEMT<sup>2</sup>), and

<sup>&</sup>lt;sup>1</sup>Complementary Metal Oxide Semiconductor

<sup>&</sup>lt;sup>2</sup>Pseudomorphic High Electron Mobility Transistor

micromachined capacitors (RF-MEMS<sup>3</sup>).

The  $Q(\eta)$  trade-off at frequencies mainly between 0.5–2 GHz will be discussed for different tunable or switchable devices. In order to beat this trade-off coming up with new ideas could be essential. Simple 1-D device models are employed, assuming the devices are optimized, with key data of the Q and  $\eta$  from literature of each device technology, to present the state of the art.

The devices and technologies are difficult to compare: Measurement conditions and design vary from case to case.  $Q(\eta)$  curves for various conditions (breakdown, frequency or voltage) are presented here. However, we give generic comparison figures based on general physical principles wherever possible. The state of the art of the  $Q(\eta)$  of each technology will be given in the discussion.

This Chapter is subdivided as follows. In Section 2.2 we discuss the operation principle, the corresponding loss-model and design considerations to improve the device performance with key  $Q(\eta)$  data from literature. The lowest quality factor over the tuning range is given throughout this section. In Section 2.3 the state of the art  $Q(\eta)$  of each technology is given, compared and discussed. Then, in Section 2.4 the conclusions are drawn. Finally, in Section 2.5 the motivation of why studying the potential of dielectric varactors at RF is addressed.

#### 2.2 Technologies

For each technology in this literature study, parallel-plate capacitors are employed. The parallel-plate capacitance is expressed by

$$C = \frac{\varepsilon_0 \varepsilon_r A}{b} \tag{2.1}$$

with the permittivity of free space  $\varepsilon_0 = 8.85 \cdot 10^{-12} \,\mathrm{F/m}$ , relative permittivity  $\varepsilon_r$  (also in literature indicated as 'kappa'  $\kappa$ ) of the dielectric material between the plates, plate area A and the distance h between the plates. The capacitance can be varied

<sup>&</sup>lt;sup>3</sup>Radio Frequency Micromachined Electro Mechanical System

- 1. in varicaps via a change in the depletion layer width  $h_{\rm vc}$  in the semi-conductor,

- 2. in dielectric varactors through a change in  $\varepsilon_{\rm r}$ ,

- 3. by a combination of switches and capacitors, and

- 4. in RF-MEMS capacitors by a change in the distance  $h_{\rm mems}$  between the two electrodes (planar capacitor) or a change in the effective electrode overlapping area A (comb-like structures), or by a moveable dielectric.

Below, these four approaches are elaborated in detail.

#### 2.2.1 Varicaps

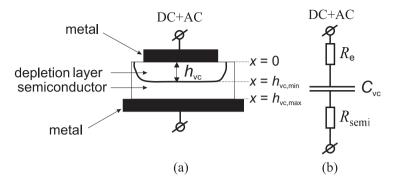

Varicaps or varactor diodes are the most widely used type of electrically continuously tunable capacitors [12]. The capacitance can be tuned by varying the depletion layer width  $h_{vc}$  due to a change in DC bias, which is superimposed on an AC signal. A schematic cross-section is depicted in Figure 2.1a, and the loss model is based on the physical operation principle and is shown in Figure 2.1b. The interconnect losses and electrode losses are given by  $R_{e}$ , the capacitance of the varicap by  $C_{vc}$  and the resistance of the semiconductor by  $R_{semi}$ .

An increase in DC bias increases the depletion layer width, which (in case of a Schottky varicap) starts from below the top electrode, reducing the capacitance. The minimum and maximum depletion layer width and the breakdown voltages for silicon (Si) and galium arsenide (GaAs) are calculated using the following formulas in S.M. Sze and K.K. Ng [13] for single-sided abrupt p-n junctions.

The minimum depletion layer width

$$h_{\rm vc,min} = \sqrt{\frac{2\varepsilon_0\varepsilon_{\rm S}}{qN}(\psi_{\rm bi} - \frac{2kT}{q})}$$

(2.2)

with  $\varepsilon_{\rm S}$  the relative permittivity of the semiconductor, the elementary charge  $q=1.6\cdot 10^{-19}\,{\rm C}$ , the doping concentration N in cm<sup>-3</sup>, the built-in voltage  $\psi_{\rm bi}=0.75$ , the Boltzmann constant  $k=1.38\cdot 10^{-23}\,{\rm J/K}$ , and the temperature  $T=300\,{\rm K}$ .

Figure 2.1 – (a) a schematic cross-section of a Schottky varicap. The depletion layer  $h_{\rm vc}$  is controlled by the electric field and determines the capacitance value. In (b) the loss-model is shown based on physical operation principles. The interconnect losses and electrode losses are given by  $R_{\rm e}$ , the capacitance of the varicap by  $C_{\rm vc}$  and the resistance of the semiconductor by  $R_{\rm semi}$ .

The maximum depletion layer

$$h_{\text{vc,max}} = \sqrt{\frac{2\varepsilon_0 \varepsilon_S}{qN} (\psi_{\text{bi}} + V_{\text{rev.,max}} - \frac{2kT}{q})}$$

(2.3)

with the maximum reverse breakdown voltage  $V_{\text{rev.,max}}$ .

In the case of uniformly doped Si

$$V_{\text{rev.,max,Si}} = \frac{E_{\text{c}}h_{\text{vc,max}}}{2} = \frac{\varepsilon_0 \varepsilon_{\text{r,Si}} E_{\text{c,vc Si}}^2}{2qN}$$

(2.4)

with  $\varepsilon_{\rm r,Si} = 11.7$ , and in the case of GaAs

$$V_{\text{rev.,max,GaAs}} = 60(\frac{E_{\text{g,GaAs}}}{1.1})^{1.5}(\frac{N}{10^{16}})^{-0.75}$$

(2.5)

with  $\varepsilon_{\rm r,GaAs} = 12.9$  and the bandgap energy  $E_{\rm g,GaAs} = 1.424\,{\rm eV}$ .

The critical electric field or maximum electric field at breakdown in Si can be described as

$$E_{\text{c,vc Si}} = \frac{4 \cdot 10^5}{1 - \frac{1}{3} \log_{10}(\frac{N}{10^{16}})}$$

(2.6)

for a uniform doping concentration. In general, a non-uniform doping profile is chosen. A heavily doped single-sided, i.e., hyper-abrupt, varicap is often employed [14], which supports a large change in depletion-width and hence results in a higher Q and  $\eta$ . A large tuning range requires a large change in depletion-width and thus a large series-resistance (low Q due to lowly doped semiconductor) for the minimum depletion state. This trade-off becomes [11, 15]

$$\frac{1}{Q} = \omega C_{\text{vc,max}} R_{\text{semi}} = \frac{\omega \varepsilon_0 \varepsilon_r}{h_{\text{vc,min}}} \int_{h_{\text{vc,min}}}^{h_{\text{vc,max}}} \rho(x) dx$$

(2.7)

with  $\omega$  the angular frequency,  $C_{\text{vc,max}}$  the maximum capacitance of the varicap at  $h_{\text{vc,min}}$ ,  $R_{\text{semi}}$  the resistance of the semiconductor, and the resistivity of the epi-layer

$$\rho(x) = \frac{1}{N(x)q\mu_{\rm p}} \tag{2.8}$$

with the electron mobility  $\mu_{\rm n}$  in cm<sup>2</sup>/V·s and the depth of the doping profile x. The loss is modeled by interconnect and electrode losses ( $R_{\rm e}$ ), the resistance of the semiconductor material  $R_{\rm semi}$  and by a capacitor (see Figure 2.1b).  $R_{\rm e}$  can be minimized by using thick metals and substrate-transfer techniques [16].  $R_{\rm semi}$  is obtained by integrating  $\rho(x)$  from  $h_{\rm vc,min}$  to the backside electrode. The well conducting backside electrode should begin at  $h_{\rm vc,max}$ . Finally, the dependencies can be inserted in equation 2.10.

Inserting a power-law doping profile

$$\rho(x) = \rho(h_{\text{vc,min}}) \left(\frac{x}{h_{\text{vc,min}}}\right)^n \sim x^n$$

(2.9)

in equation 2.7 results in

$$Q^{-1} = \omega \varepsilon_0 \varepsilon_r \rho(h_{\text{vc,min}}) \frac{(\eta^{n+1} - 1)}{(n+1)} \quad \text{with} \quad \eta = \frac{C_{\text{vc,max}}}{C_{\text{vc,min}}} = \frac{h_{\text{vc,max}}}{h_{\text{vc,min}}}.$$

(2.10)

Two special cases, namely n=0 [17] and n=2 [15], can be used for low distortion arrangements.

When n=0 a uniform, i.e. abrupt, doping profile is obtained and for  $n \gg 0$  a hyper-abrupt doping profile. A hyper-abrupt profile allows for a larger tuning range than a uniform doping profile.

The power-law doping profile enables to study two cases: 1) diodes with low distortions and 2) diodes with different doping profiles. By changing the n, the  $Q(\eta)$  of different doping profiles can be studied, so that one can

see how much improvement can be obtained, e.g., by comparing the tuning of an abrupt to a hyper-abrupt diode.

The product  $\varepsilon_0 \varepsilon_r \rho(h_{\text{vc,min}})$  can be regarded as a figure of merit. The (maximum) conductivity  $\rho(h_{\text{vc,min}})$  is limited by the maximum achievable dopant concentration just before breakdown or tunneling occurs (see further in this section). An excellent value of  $\varepsilon_0 \varepsilon_r \rho(h_{\text{vc,min}}) = 4 \text{ fs seems achievable with very high peak doping levels of up to <math>10^{18} \text{ cm}^{-3}$  in Si [15].

Equation 2.10 yields the  $Q(\eta)$  function for a given doping profile. The tuning range of a given diode could be traded off for the quality factor if only a part of the tuning range is used, namely between breakdown and a (non-zero) reverse bias.

Another option is to connect a high-quality-factor fixed capacitor in series, as is anyhow needed in many applications which require a bias voltage. In this case the trade-off is of the same form as described by equation 2.10 with n=0 for any doping profile. However, the best trade-off  $Q(\eta)$  will be obtained if the dopant concentration is optimized for each maximum tuning ratio  $\eta_{\rm max}$  separately. The following paragraph describes the calculation for abrupt (n=0) Si and GaAs varactors based on the doping dependence of the breakdown field and conductivity.

The conductivity was calculated from the mobility using the empirical model of G. Masetti et al. [18]

$$\mu_{\rm n} = \mu_0 + \frac{\mu_{\rm max} - \mu_0}{1 + (N/C_{\rm R})^{\alpha}} - \frac{\mu_1}{1 + (C_{\rm S}/N)^{\beta}}$$

(2.11)

for arsenic doping suited from  $N = 10^{13} - 5 \cdot 10^{21} \, \mathrm{cm}^{-3}$  in Si (highest mobility). The fit parameters  $\mu_{0,\mathrm{Si}} = 52.2 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$ ,  $\mu_{\mathrm{max,Si}} = 1417 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$ ,  $\mu_1 = 43.4 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$ ,  $C_{\mathrm{R}} = 9.68 \cdot 10^{16} \, \mathrm{cm}^{-3}$ ,  $C_{\mathrm{S}} = 3.43 \cdot 10^{20} \, \mathrm{cm}^{-3}$ ,  $\alpha = 0.68$ , and  $\beta = 2$ .

The same model was fitted to the data for GaAs, taken from Figure 18 in reference [13]. The fit parameters are  $\mu_{0,\text{GaAs}} = 1900 \,\text{cm}^2/\text{V} \cdot \text{s}$  and  $\mu_{\text{max,GaAs}} = 7600 \,\text{cm}^2/\text{V} \cdot \text{s}$ . The remaining parameters to determine the mobility were left constant as in [18].

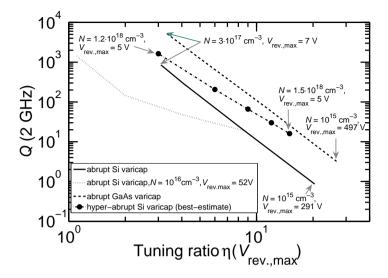

The results are the dependencies of the quality factor Q and the maximum tuning ratio  $\eta$  on the dopant concentration N, which are parametrically plotted in Figure 2.2 for abrupt Si and GaAs diodes.

Increasing the dopant concentration increases the quality factor, but low-

Figure 2.2 – Calculated data of the trade-off between quality factor Q and maximum tuning ratio  $\eta$  for idealized, one dimensional varactor diodes 2 GHz. The solid line denotes abrupt Si varactors, the dashed line abrupt GaAs varactors, and the dash-dotted line hyper-abrupt varactors. The corresponding dopant concentrations N and reverse breakdown voltages  $V_{\rm rev.,max}$  are attached to selected points on the lines. The dotted line shows an abrupt Si varactor with fixed dopant concentration of  $10^{16} {\rm cm}^{-3}$ , where only a part of the tuning range is used by demanding a minimum bias voltage.

ers the breakdown voltage and hence the tuning range. If the dopant concentration is very high, tunneling can occur at the junction, so that the tuning range is further reduced. In Si(Ge) this will occur above  $N > 3 \cdot 10^{17} \,\mathrm{cm}^{-3}$  [19]. The curves are therefore plotted till this level. The lowest dopant concentration was chosen so that Q was in the range of 1–10. The calculated  $Q(\eta)$  data for Si is close to what is postulated by the International Technology Roadmap for Semiconductors from 2012 on [20]: Q > 50 at 5 GHz (corresponds to Q > 125 at 2 GHz) for  $\eta > 5.5$ .

The functional dependence of  $Q(\eta)$  from equation 2.10 can be approximated by  $1/Q \sim \eta^{n_a+1}$  with  $n_a=2.6$  for Si for  $\eta \approx 4$ –10 and  $n_a=2.67$  for GaAs for  $\eta > 4$ , with ' $n_a+1$ ' the relevant slope in Figure 2.2. The doping dependence of the mobility has been obtained by fitting it with a power law and assuming large tuning ratios. It should therefore fit best to low dopant concentrations. Although in equation 2.10 the optimization of the breakdown voltage has not been taken into account, it can fit the results by using a modified exponent

$n \approx 2.6$  instead of n = 0 for abrupt varactor diodes. This confirms that optimizing a diode for the needed tuning range is better than reducing the tuning range by using only a part of the C(V) curve. The second case is also plotted in Figure 2.2.

Hyper-abrupt varactor diodes can be optimized for the maximum tuning range not only by the doping level, but also by the shape of the doping profile. Such a study was undertaken by C. Huang et al. for n=2 [15]. The best reported values for a constant reverse breakdown voltage of 5 V are plotted in Figure 2.2. All data points have a maximum dopant concentration of ca.  $10^{18} {\rm cm}^{-3}$  at the junction. A higher reverse voltage does not necessarily lead to a better  $Q(\eta)$  trade-off for the higher tuning ratios [15]. The resulting  $Q(\eta)$  curve can also be fitted by equation 2.10 with  $n \approx 2$  and  $\varepsilon_0 \varepsilon_r \rho(d_{\min}) \approx 4 \, {\rm fs}$ .

Hyper-abrupt varactors can have a better  $Q(\eta)$  trade-off, but the functional shape of the trade-off is similar to that of abrupt Si diodes. The performance of hyper-abrupt GaAs varactor is expected to be higher than that of Si, analogous to abrupt varactor diodes. It should be noted that for high quality factors (Q>100) additional losses from the electrode connections become important.

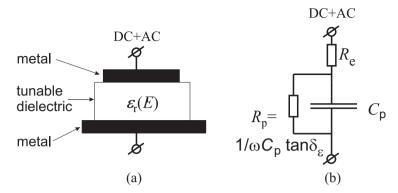

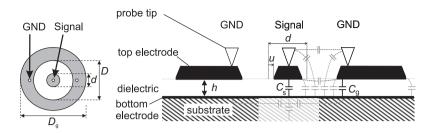

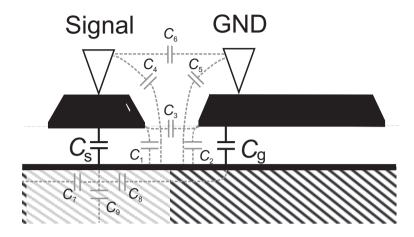

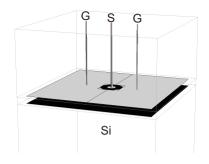

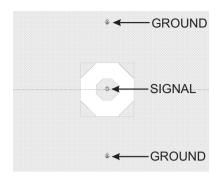

#### 2.2.2 Dielectric varactors

Another type of continuously tunable capacitors is the dielectric varactors. The permittivity changes when a voltage is applied to the capacitor. This varactor is the smallest tunable capacitors due to its high permittivity, e.g, the  $\varepsilon_{\rm r}$  of a semiconductor material ( $\approx 12$ ) is typically much smaller than the  $\varepsilon_{\rm r}$  of a ferroelectric material (typically > 100). The parallel plate metal-insulator-metal (MIM) capacitor (see Figure 2.3) has low fringing fields, a high capacitance density and a low tuning voltage [7].

The relative permittivity of some materials, notably those with a high permittivity like ferroelectrics, e.g.,  $Ba_xSr_{1-x}TiO_3$  (BST), changes by applying a non-zero DC bias field due to the saturation of the dielectric polarization [21]. A higher electric field decreases the permittivity.

Non-ferroelectric, but nevertheless tunable dielectrics with a high permittivity exist, e.g., with a pyrochlore phase like Bi<sub>1.5</sub>Zn<sub>1.0</sub>Nb<sub>1.5</sub>O<sub>7</sub> (BZN). Liquid crystals are representative for a tunable dielectric with a low dielectric constant [22]. However, their tuning ratio is limited to the low

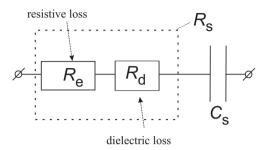

Figure 2.3 – Part (a) shows the schematic cross-section of a metal-ferroelectric-metal capacitor. A change in electric field E between the parallel metal plates changes the  $\varepsilon_{\rm r}$  of the ferroelectric. In (b) the loss-model is shown. The series resistance of the interconnect loss and electrodes is given by  $R_{\rm e}$ , the resistivity of the dielectric by  $R_{\rm p}$  and the ferroelectric capacitance by  $C_{\rm p}$ .

maximum relative permittivity. The tuning ratio in these components is  $\varepsilon_{\rm r,max}/\varepsilon_{\rm r,min}$  [23].

The capacitance of the tunable dielectric  $C_{\rm p}$  is not ideal. The dielectric loss  $\tan \delta_{\epsilon}$  (see Section 3.3), and the interconnect and electrode resistance  $(R_{\rm e})$  cause dissipation (Figure 2.3). The series resistance of the interconnects can be minimized by small patterns and thick metals with a high conductivity. The latter also holds for the electrodes.

Ferroelectric materials are mainly used in their paraelectric state in the temperature region above the Curie temperature [24], because of lower losses. The tuning ratio in the ferroelectric phase, which exists in the temperature region below the Curie temperature, is higher, at the cost of higher losses due to irreversible domain wall movements [24, 25].

Since ferroelectric materials have piezoelectric or electrostrictive properties [24], a bulk acoustic wave [26,27] is excited when a DC electric field is applied [28]. The layers of the capacitor should be chosen in such a way that the acoustic wave is suppressed at the operating frequency. Alternatively the materials can be used for acoustic filters [29], which could even be tunable [30–33].

The high non-linear permittivity of most tunable dielectrics is caused by atomic displacements [34]. Acoustic losses due to the phonon excitation by the atomic movements are the limiting (intrinsic) loss factor [23]. First, a simple model for the intrinsic losses is given. Then a phenomenological  $Q(\eta)$

is proposed based on literature data that includes extrinsic losses, e.g., by defects in the thin layers.

Assuming a bias-field-induced Quasi-Debye mechanism for the intrinsic losses a trade-off

$$Q^{-1} = \omega \tau_{\rm d}(\eta - 1)$$

, with  $\tau_{\rm d} = A_{\rm deb} I_{\rm deb}(E_0)$  (2.12)

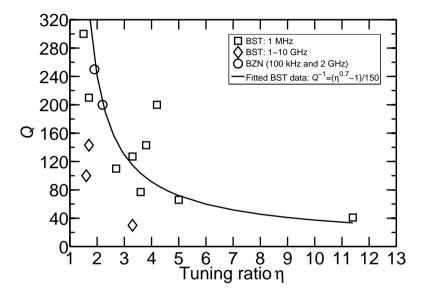

can be derived between the quality factor Q and the tuning ratio  $\eta$  [23, 35]. The angular frequency  $\omega$  should be well below the phonon damping frequency (ca. 100 GHz) [23, 35]. The parameter  $I_{\rm deb}$  [23, 35] depends on the tuning field  $E_0$  and is in the order of 1 for small fields (tuning ratio  $\eta$  close to 1). The parameter  $A_{\rm deb}$  is expected to be in the order of magnitude of 1000 fs [23, 35]. The measured literature data from Figure 2.4 above 1 GHz correspond to values of  $\tau_{\rm d} = 100-2000$  fs.

Equation 2.12 predicts the highest losses at high tuning field, because then the acoustic coupling is strongest. Single crystalline materials often follow this behavior. However, many thin film measurements show the opposite dependence. The losses are lowered at high fields. Defects, stress distributions, interfaces or a resistive electrode design are possible causes for this behavior.

In general, careful processing measures should be taken to minimize bad interface layers to the film, porosity and cracks, which could decrease Q. A thin dead layer (an unintentional low  $\varepsilon_r$  dielectric layer between 1 or more electrodes and the high  $\varepsilon_r$  ferroelectric layer) also reduces the tuning ratio. The capacitive test structures should be small in physical size to increase the Q of high permittivity ferroelectric capacitors, as discussed in [36].

The capacitance and quality factor are frequency dependent due to dielectric relaxation (see Chapter 3). The relaxation current density  $J_{\rm r}$  versus time t of real ferroelectric devices after a voltage step follows a power-law dependence, denoted as the Curie-von Schweidler behavior [37,38], which can be expressed as

$$J_{\rm r}(t) = J_0(E) \cdot t^{-(\beta+1)} \tag{2.13}$$

with  $J_0(E)$  a field-dependent parameter, and with  $0 < \beta < 1$ . The time-dependent polarization relaxation exhibits itself as the dispersion in quality factor with respect to frequency [39]

$$Q \sim \omega^{-\beta},\tag{2.14}$$

a less severe frequency dependence than predicted by a Debye model [37]. Limited experimental data for BST and BZN show frequency dependencies  $\beta$  even below 0.1–0.33 [38, 40, 41]. Therefore a phenomenological approach was chosen.

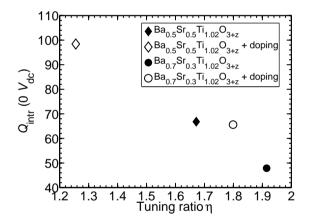

Figure 2.4 – The results are based on a literature survey on the performance of dielectric parallel plate MIM varactors in terms of Q and  $\eta$ . The solid line is a fit to the best reported measurement results of ferroelectric varactors (Ba<sub>x</sub>Sr<sub>1-x</sub>TiO<sub>3</sub> (BST), squares) at 1 MHz [40–48]. Data of BST for 1–10 GHz are plotted as diamonds [40,41]. The  $Q(\eta)$  literature data of varactors based on the nonferroelectric dielectric BZN are indicated by circles [49, 50]. The BST data indicate that Q decreases when  $\eta$  increases.

Data on thin film ferroelectrics, using different deposition techniques, which have resulted in a high tunability and low losses were collected for parallel plate MIM capacitors at 1 MHz for  $\text{Ba}_{\mathbf{x}}\text{Sr}_{1-\mathbf{x}}\text{TiO}_3$  (BST) [40–48]. Data of BST between 1–10 GHz is given in [40] and [41]. For the non-ferroelectric dielectric BZN, data is indicated in [49,50]. Many more papers exist on microwave losses in thin dielectric films, but only papers were chosen with the best  $Q(\eta)$  values of parallel plate MIM capacitors with electrodes that are realistic for miniaturized devices.

If the assumption is made that the losses of dielectric varactors will only slightly increase with frequency following a Curie-von Schweidler law after Fourier transform (see equation 2.14), then the low frequency results pose an upper limit to the high frequency performance (see Figure 2.4).

Experimental results show a weaker dependence of Q on  $\eta$  than equation 2.12 predicts. We attribute the difference to the significance of extrinsic losses in polycrystalline material.

The low frequency  $Ba_xSr_{1-x}TiO_3$  data can be fitted by

$$Q^{-1} = (\eta^{0.7} - 1)/150 (2.15)$$

(see Figure 2.4). Data at microwave frequencies in some cases come close to the low frequency data. This is another indication that the losses are still dominated by extrinsic losses and less by intrinsic losses as described by equation 2.12.

The  $Q(\eta)$  plot shows the limiting (fitted) curve of what could be achieved if the tuning field is increased up to breakdown. The data suggests there is still room for improvement by reducing the extrinsic defects.

#### 2.2.3 Semiconductor-switched capacitors

Semiconductor components such as PIN-diodes, CMOS switches and pHEMT switches offer high performance at RF frequencies. PIN-diodes dissipate considerable power in the on-state and are therefore left out in this study, although they can have a good high-frequency performance.

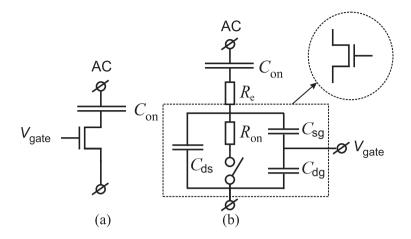

A transistor-switched capacitor is basically a transistor in series with a non-tunable (linear) capacitor or a tunable capacitor (see Figure 2.5).

In Figure 2.5 the drain-source capacitance is expressed as  $C_{\rm ds}$ , the source-gate capacitance as  $C_{\rm sg}$ , and the drain-gate capacitance as  $C_{\rm dg}$ . The off capacitance is expressed as [52]

$$C_{\text{off}} = \frac{C_{\text{sg}}C_{\text{dg}}}{C_{\text{sg}} + C_{\text{dg}}} + C_{\text{ds}}.$$

(2.16)

Typically, a non-tunable MIM capacitor is used due to its higher Q-factor. High-quality MIM capacitors are available that have negligible small losses with respect to the losses of the switch. Such capacitors have dielectrics

Figure 2.5 – In (a) a schematic picture of a transistor in series with a capacitor is given. If sufficient gate bias  $V_{\rm gate}$  is applied on the transistor, a channel is formed between the source and drain, and the capacitor is connected to the circuit [51]. In (b) the loss-model of the transistor-switched capacitor is depicted [51, 52]. When the switch is closed,  $R_{\rm on}$  dominates the performance. When the switch is open, the off-capacitance  $C_{\rm off}$  (see equation 2.16) dominates the minimum capacitance. The capacitance  $C_{\rm on}$  is assumed to be an ideal capacitor, e.g., a low loss MIM capacitor.

with a low dielectric constant and low losses, such as  $SiO_2$ ,  $Si_3N_4$  or  $Al_2O_3$  and are connected with highly conducting electrodes such as, e.g., Al or Cu. The transistor is employed to switch a capacitor on/off. In the off-state the parasitic capacitance of the switch determines the minimum capacitance value. In the on-state the transistor resistance determines the Q of the switch-capacitor configuration.

We assume that the switch is connected to an ideal capacitor. Varying its value yields the trade-off between the tuning ratio  $\eta$  and the quality factor Q in the on-state. In the model presented in Figure 2.5 the on-state yields a lower Q than the off-state, so that we take the lower value in the on-state for the comparison. A low on-resistance  $R_{\rm on}$  is thus crucial for a high Q switched capacitor array.

In this section, we discuss CMOS and pHEMT switches. We assume  $R_{\rm on} \gg R_{\rm e}$ . The  $Q(\eta)$  trade-off for CMOS and pHEMT switches becomes

$$Q^{-1} = \omega R_{\rm on} C_{\rm off}(\eta - 1),$$

(2.17)

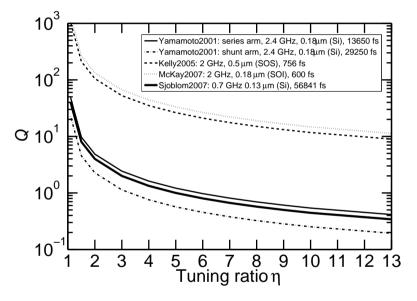

which is the same expression as for uniformly doped varicaps. Equation 2.17 is utilized to plot literature data from

- 1. CMOS switches, on  $0.13 \,\mu\text{m}$  Si at  $0.7 \,\text{GHz}$  [53], on  $0.18 \,\mu\text{m}$  Si at  $2.4 \,\text{GHz}$  [54], on  $0.18 \,\mu\text{m}$  silicon-on-insulator (SOI) at  $2 \,\text{GHz}$  [55] and on  $0.5 \,\mu\text{m}$  silicon-on-sapphire (SOS) [51], and

- 2. pHEMT switches, on 0.5  $\mu$ m GaAs at 2 GHz [51], and on 0.15  $\mu$ m and 0.5  $\mu$ m GaAs at 0.9 GHz [52]

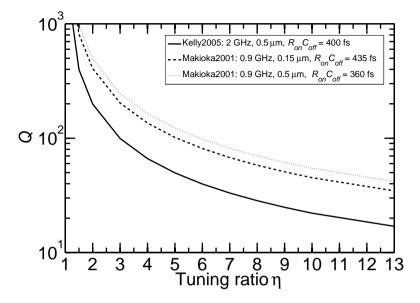

in Figures 2.6 and 2.7, respectively. The best figures of merit  $R_{\rm on}C_{\rm off}$  are reported for the case of a 0.5  $\mu$ m CMOS-switch on Sapphire  $R_{\rm on}C_{\rm off,CMOS} = 750$  fs [51] and a 0.5  $\mu$ m pHEMT switch  $R_{\rm on}C_{\rm off,pHEMT} = 360$  fs [56].

Figure 2.6 – The performance of CMOS switches in terms of Q and  $\eta$  at 0.7 GHz (0.13 μm Si,  $R_{\rm on}C_{\rm off}=56841$  fs [53]), 2 GHz (0.18 μm SOI,  $R_{\rm on}C_{\rm off}=600$  fs [55] and 0.5 μm SOS,  $R_{\rm on}C_{\rm off}=756$  fs [51]) or 2.4 GHz (0.18 μm Si,  $R_{\rm on}C_{\rm off}=13650$  fs (series arm) and 29250 fs (shunt arm) [54]) based on a literature survey. The experimental data from literature are for Si, silicon-on-insulator (SOI) or silicon-on-sapphire (SOS) substrates. The products of  $R_{\rm on}C_{\rm off}$  of the CMOS switches from literature are filled in equation 2.17, which results in the curves above. The Q decreases with increasing η.

In CMOS switches N-channel MOSFETS are preferred because of a low  $R_{\rm on}$ . The width of the channel needs to be optimized [57]. A large width

Figure 2.7 – The performance of pHEMT switches in terms of Q and  $\eta$  at 0.9 (0.15  $\mu$ m and 0.5  $\mu$ m [52]) or 2 GHz (0.5  $\mu$ m [51]) based on equation 2.17 and a literature survey. The measurement results from literature are performed on Si, silicon-on-sapphire (SOS) and on SOI substrates. The product of  $R_{\rm on}C_{\rm off}$  shown in the Figure are filled in equation 2.17 which results in the curves above. The Q decreases with increasing  $\eta$ .

reduces  $R_{\text{on}}$  and increases Q to a certain extent. When the width becomes too large, then the capacitive coupling to the substrate reduces Q.

In pHEMT switches the channel doping decreases the  $R_{\rm on}$  at the cost of additional parasitic capacitance between the source and drain reducing the isolation in the off-state [58].

#### 2.2.4 RF-MEMS

RF-MEMS [59] contain movable parts and can be configured as miniaturized (galvanic) relays or continuously tunable capacitors. These switches have a relatively large physical size [60], compared to the other devices discussed earlier, due to the actuator that moves the mechanical parts. Galvanic RF-MEMS switches are similar to semiconducting switches and will be briefly discussed at the end of this section. In capacitive RF-MEMS switches the geometry of a capacitor is varied. A compact version, although still relatively

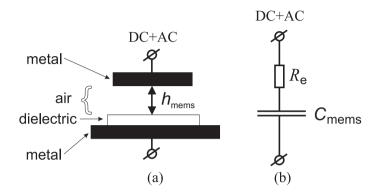

large compared to other tunable technologies, e.g., ferroelectric capacitors, due to the low  $\varepsilon_{\rm r}$ , is a planar electrostatic RF-MEMS capacitive switch, where the RF capacitor is also the electrostatic actuator (see Figure 2.8).

Figure 2.8 – In (a) the schematic cross-section of a planar RF-MEMS electrostatic switched capacitor is shown. The dielectric layer prevents a short-circuit between the top electrode and the bottom electrode. The distance  $h_{\rm mems}$  between the top electrode and the dielectric determines the value of the capacitance and is controlled by the electric field. In (b) the loss-model is given and is based on physical operation principles. The interconnect and resistive electrode loss is given by  $R_{\rm e}$  and the capacitance of the planar RF-MEMS capacitive switched capacitor by  $C_{\rm mems}$ .

The capacitance is tunable by varying the distance  $h_{\rm mems}$  between the top electrode and the dielectric, by a DC bias stimulus superimposed on an AC signal, or by a separate actuator. This principle also holds for vertical 3D MEMS like comb-structures. The combs move in-plane and vary the overlap area of the electrodes.

IDC capacitors in MEMS technology have low parasitic capacitances due to the use of air as a dielectric, and the interdigitated fingers have a very large aspect ratio, so that they become 90-degree tilted 'MIM capacitors'. Rotational movement like in manual trimming capacitors is less suited for integration on wafer level due to a lack of bearings, but can be integrated vertically [61].

J-B. Yoon and C.T.-C. Nguyen [62] designed an RF-MEMS, which can move a dielectric horizontally between two parallel plates. Measurements on prototypes of this design show a Q of 218 at 1 GHz with a tuning range of 40 %  $(\eta \approx 2)$ . The 'movable dielectric' devices are limited in tuning range due to the air gap.

There is no fundamental difference in gap tuning, area tuning and move-

able dielectric tuning, since the dielectric layer (air or vacuum) is basically lossless and the electrode and anchor losses dominate performance of unpackaged planar RF-MEMS capacitively switched devices. In principle, the planar RF-MEMS capacitive switched capacitor has no trade-off between quality factor and tuning ratio. But it has practical limitations. The equivalent circuit is shown in Figure 2.8.

The dielectric losses for common insulators, in planar RF-MEMS electrostatic capacitive switches, such as  ${\rm SiO_2}$  and  ${\rm Si_3N_4}$  are negligible ( $\tan\delta < 0.003$  is certainly feasible). The main losses therefore come from the resistive electrodes, whereas in the other discussed technologies the inherent losses add to, or often dominate over the electrode losses.

The trade-off between a practical actuator and the capacitor design induces a trade-off between Q and  $\eta$ . One of the typical bottlenecks are the electrode connections to the movable electrode ('anchors'). They need to be well conductive, but at the same time they must be flexible to allow movements. H.S. Lee et al.[63] circumvented this by using an electrically floating top plate and two separate planar bottom plates. Two capacitors are measured in series from the floating top plate to the bottom plates. The signal pad goes via the substrate without passing through the mechanical springs. The capacitance varies between 300–430 fF,  $Q \approx 70$  at 2 GHz and  $\eta = 1.7$  at 5 GHz.

Smaller planar RF-MEMS capacitive switches need narrower or thinner connections when the tuning ratio and the actuation is kept constant. But it also has a lower capacitance, so that the quality factor is not strongly dependent on the size of the planar capacitive RF-MEMS switch, but rather on the gap that needs to be closed. A larger gap yields a higher anchor resistance at a given actuation voltage. A large gap is equivalent to a large tuning ratio. The electrode surface roughness additionally affects the maximum capacitance when closed  $(C_{\rm max})$  and should be low [64] to yield a high tuning ratio.

Parasitic effects, such as coupling to the substrate, are of course also important and are normally strongly reduced by isolating substrates. For a best estimate those effects are neglected here. Then  $R_{\rm e}$  and  $C_{\rm MEMS,max}$  are the crucial parameters and the quality factor is expressed by

$$Q^{-1} = \omega R_{\rm e} C_{\rm mems, max} = \omega R_{\rm e} C_{\rm mems, min} \eta$$

(2.18)

with the resistance  $R_{\rm e}$  of the electrodes. The measurement data from literature [61, 63, 65–68] differ in some cases from 2 GHz, but are in the range of 0.5–5 GHz.

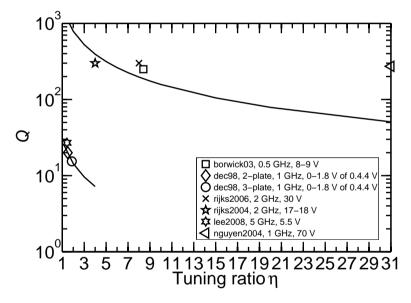

A Q of 300 has been measured at 2 GHz with a tuning ratio of 8 at a maximum actuation voltage of 17 V and a nominal capacitance of 0.47 pF [68], yielding  $R_{\rm e}C_{\rm mems,min}=33$  fs. The data from literature in combination with equation 2.18 give a benchmark for planar RF-MEMS capacitive electrostatic switches.

The RF-MEMS electrostatic capacitive switch shows a high Q across the tuning range at 2 GHz. The trade-off between the Q and  $\eta$  for these devices are visualized in Figure 2.9 for gap-tuned capacitive RF-MEMS devices, since these devices uphold the highest performance.

Figure 2.9 – The results are based on equation 2.18 and a literature survey on the  $Q(\eta)$ -performance of planar RF-MEMS electrostatic capacitive switches between 0.5–5 GHz [61, 63, 65–68]. The actuation voltage, and operating frequency differs in some cases from 2 GHz since not all measurements in literature are performed the same. Measured data points of capacitive RF-MEMS devices using the gap tuning principle are shown; except for 'nguyen2004' [61] which uses vertical combdriven angular capacitors with fairly large actuators. Two trendlines are indicated for lower and higher actuation voltages. The Q decreases with increasing  $\eta$ .

The performance close to Q=20 shows that the Q decreases with  $\eta$ . Planar RF-MEMS capacitive switches with a higher  $Q(\eta)$  performance close to

Q = 300, also show the same decrease. Two trendlines have been drawn for both groups of datapoints.

Galvanic RF-MEMS switches make or break an Ohmic contact as a relay. Their equivalent circuit can be compared to the simplified model for semiconducting switches in Figure 2.5. An ideal fixed capacitor is connected to the galvanic MEMS switch. The on-resistance is a sum of the resistance of the anchors and the resistance of the contact. A capacitive RF-MEMS switch with the same size of a galvanic RF-MEMS switch can therefore have a lower series resistance. But on the other side there is the advantage of a lower off-capacitance because of the small contact area.

The size of the galvanic MEMS is mainly determined by the size of the actuator. A large actuator can induce a high contact force and ensure a low on-resistance. A trade-off on the size of the switch is therefore expected. This is also reflected in Figure 2.9. A lower actuation voltage or smaller size leads to a higher loss.

One of the best reliable galvanic MEMS switches [69], which is still fairly large, achieves a figure of merit of  $R_{\rm on}C_{\rm off}\approx 30\,{\rm fs}$ . This is in the same order of magnitude as planar capacitive RF-MEMS and clearly demonstrates the performance potential of planar RF-MEMS capacitive switches.

#### 2.3 Discussion

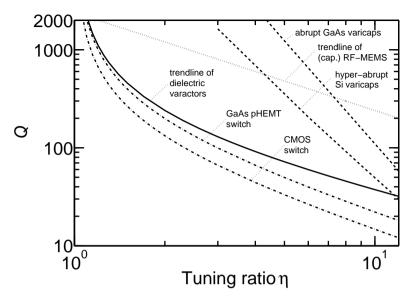

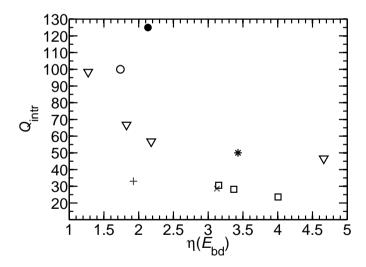

The state of the art performance in terms of  $Q(\eta)$  of each tunable and switchable technology is combined and summarized in Figure 2.10. Experimental  $Q(\eta)$  results of dielectric parallel plate varactors are fitted. For varactor diodes the limiting simulations are given.

For practical reasons a transistor-capacitor switchable array is preferred in the high tuning regime (including parasitics) and best realized by pHEMT and CMOS. Although, RF-MEMS capacitive switches offer even a higher tuning ratio, they are less mature and less widely available. For the lower tuning ranges diodes offer higher performance. The values of CMOS and pHEMT switches are somewhat worse compared to varicaps due to the parasitic capacitances at the channel.

RF-MEMS capacitive switches offer a low loss with a high tuning ratio as well as digital operation. For the latter, a large physical size and a relatively small capacitance value, due to hermetic packaging constraints,

Figure 2.10 – The state of the art intrinsic quality factor Q at 2 GHz without interconnects versus the tuning ratio  $\eta = C_{\rm max}/C_{\rm min}$  limited to  $\eta = 12$ . All data are given at 2 GHz unless stated otherwise. The best data found in literature for GaAs pHEMT  $(0.5\,\mu{\rm m})$  [51] and CMOS $(0.18\,\mu{\rm m}$  SOI) switch [55] are shown with dash-dotted lines.

The solid line is a fit to the best reported measurements of ferroelectric varactors (Ba<sub>x</sub>Sr<sub>1-x</sub>TiO<sub>3</sub>) at 1 MHz. The trend line also overlaps the data points of nonferroelectric Bi<sub>1.5</sub>Zn<sub>1.0</sub>Nb<sub>1.5</sub>O<sub>7</sub> at 100 kHz and 10 GHz. The dashed lines represent the  $Q(\eta)$  response of ideal abrupt GaAs varicaps with  $N=10^{15}$ –3·10<sup>17</sup> cm<sup>-3</sup> and respectively  $V_{\rm rev.,max}=497$ –7 V, and the best-estimate of a hyper-abrupt Si varicaps with  $N=10^{18}$  cm<sup>-3</sup> at  $V_{\rm rev.,max}=5$  V [15].

The dotted line is the trendline for higher actuation voltages for planar RF-MEMS electrostatic capacitive switches assuming that the loss and tuning are proportional to the maximum capacitance [68].

results in a limited capacitance density. J-B. Yoon and C.T.-C. Nguyen [62] who designed and measured on a MEMS device with a movable dielectric in between the plates, obtained experimental Q(eta) values which are not higher than we report in Figure 2.9. Therefore the reasoning that 'practical' devices, useful for applications, will have a trade-off still remains valid. There is no trade-off - as already stated - if the actuator can be as large as pleased.

The present state of the reliability of capacitive and a galvanic RF-MEMS switches for upcoming military and commercial applications is presented in [70].

The differences in the quality factor Q at tuning ratios below 3 become less important if the capacitors are combined with a coil. A coil typically has a Q-factor below 100 at 1–2 GHz, especially when integrated or miniaturized. The choice then depends more on other features such as size, cost and availability.

Finally, the described trade-offs can be approximated by:

$$Q^{-1} = (\omega \tau)^{\beta} (\eta^{n+1} - 1) / (n+1)$$

(2.19)

In most cases  $\beta$  equals 1, except for some extrinsic dielectric losses that scale with  $\beta < 1$ . The exponent n is a measure on how fast the quality factor drops with increasing tuning ratio  $\eta$ . It can be influenced by the device design, but is normally larger than 1. The state of the art performance of the discussed tunable technologies is depicted in Table 2.1.

| Device                    | State-of-the-art                                                | Equation | Comments                             | Ref. |

|---------------------------|-----------------------------------------------------------------|----------|--------------------------------------|------|

|                           | per formance                                                    |          |                                      |      |

| Varicap                   |                                                                 |          |                                      |      |

| Abrupt (GaAs)             | $n=0,\beta=1,$                                                  | 2.10     | $2\mathrm{GHz}$                      | [16] |

|                           | $\tau = \varepsilon_0 \varepsilon_{\rm r} \rho = 967  {\rm fs}$ |          |                                      |      |

| Hyper-abrupt              | $n=2,\beta=1,$                                                  | 2.10     | $2\mathrm{GHz},$                     | [15] |

| (Si)                      | $\tau = \varepsilon_0 \varepsilon_{\rm r} \rho = 4-6  {\rm fs}$ |          | $V_{\text{rev.,max}} = 5 \text{ V},$ |      |

|                           |                                                                 |          | modeled                              |      |

| Dielectric                | $n \approx 0, \beta < 1,$                                       | 2.19     | $2\mathrm{GHz},$                     | [11] |

| Varactor                  | $\tau_{\rm d} = 100 - 2000  {\rm fs}$                           |          | see caption                          |      |

| switched C                |                                                                 |          |                                      |      |

| CMOS                      | $n=0,\beta=1,$                                                  | 2.17     | $2\mathrm{GHz}$                      | [55] |

| $(0.18\mu\mathrm{m~SOI})$ | $\tau = R_{\rm on} C_{\rm off} = 600  \text{fs}$                |          |                                      |      |

| pHEMT                     | $n=0,\beta=1,$                                                  | 2.17     | $2\mathrm{GHz}$                      | [51] |

| $(0.5\mu\mathrm{m~GaAs})$ | $\tau = R_{\rm on} C_{\rm off} = 400 \mathrm{fs}$               |          | _                                    |      |

| capacitive                | $n=0,\beta=1,$                                                  | 2.18     | $2\mathrm{GHz}$                      | [68] |

| RF-MEMS                   | $\tau = R_{\rm e}C_{\rm min} = 33\rm fs$                        |          |                                      |      |

**Table 2.1** – The state-of-the-art performance  $\tau$  from equation 2.19 is listed together with the exponent n in the  $Q(\eta)$  trade-off. The value for the dielectric varactors is based on measured high frequency data for low tuning ratios and projections based on low frequency measurements.

Circuit designs with external low-loss capacitors therefore will not improve the  $Q(\eta)$  trade-off significantly.

Additionally, the series connection increases the breakdown voltage, but the trade-off  $Q(\eta)$  remains. For example, increasing the dielectric thickness of

the same ferroelectric MIM varactor will increase the breakdown voltage, but will not change the  $Q(\eta)$  trade-off that is fixed by the material properties of the dielectric film.

Switches can also be connected in series for higher breakdown voltage, but normally at the cost of additional parasitics. Power handling from, e.g., a  $3V_{\rm dc}$  battery can be increased with voltage converters (see, e.g., [71]). However, a low operation voltage lowers the cost and size, and makes the device more attractive for an application.

It should be stated that the above discussion outlines the general trend for the intrinsic performance. Packaging and interconnects can degrade the performance severely and must be optimized for each of the technologies within the given (cost) constraints. When a high linearity is required and higher power handling, many tuning devices can be connected in series [72, 73], which is only attractive for small devices. Switched capacitors have advantages when linearity is a priority, whereas continuously tuned devices are typically smaller than arrays of switches.

#### 2.4 Conclusions

The trade-off between losses and tuning ratio of tunable capacitors at microwave frequencies has been assessed in terms of basic physics-based models. All technologies show an increased loss for higher tuning capability and can be approximated by an equation  $Q^{-1} \sim (\eta^{n+1}-1)$  with n=-0.3-2. Planar micro-electro-mechanical capacitive switches have the highest tuning potential with a high Q, but are large. For continuous, moderate tuning ranges  $\eta < 3$ , highly doped GaAs varactor diodes could offer the best performance. Ferroelectric capacitors will be an alternative if small physical size and low cost processing are mandatory.

Besides showing the limitations of some tunable technologies, new emerging tunable technologies like tunable electro-acoustic resonators (surface acoustic waves (SAW) [74], bulk acoustic waves (BAW) [26]) are getting more attention from the research community. Acoustic waves are generated if an electric field is applied to the input port of a device containing a piezoelectric material. The electrical energy is transformed into mechanical energy [25], after which an acoustic wave is excited in the piezoelectric material resulting in a resonance. A high Q resonator in the microwave range can be obtained

if the electrode loss, the acoustic wave leakage and the mechanical loss are low [75]. However, a large tuning of the resonance frequency still remains a challenge, e.g., for  $SrTiO_3$  less than 2% [31, 76, 77],  $Pb(Zr_xTi_{1-x})O_3$  (PZT) more than 3% [30], or ZnO [78].

#### 2.5 Focus on dielectric varactors

In this work was opted for dielectric varactors as a tunable technology. Before the start of this work, ferroelectric capacitors were optimized within the company for low-frequency applications, using wet-chemical processing of lead zirconate titanate (PZT) thin films, and are currently being mass-produced, yielding a high throughput, in combination with semiconductor factory-compatible materials.

Ferroelectric capacitors in this work are based on a different ferroelectric material used for RF applications and enable a cost-effective approach (small physical area consumption, passive integration on cost-effective substrates, no hermetic package, relatively fast wet-chemical processing, processing experience exist within the company, and re-use of semiconductor factory fabrication equipment).

The potential at RF was assessed, based on a number of important pillars:

- 1. reconfigurable continuous (low-voltage) tuning (typically  $< 40 V_{dc}$ ),

- 2. high capacitance density (typically  $\varepsilon_r = 100-1000$ , small physical area, thin films, integrated decoupling [8]),

- 3. a good temperature stability of the  $\varepsilon_{\rm r}$  is feasible, and

- 4. no moving parts.

In Chapter 3 an introduction is given on dielectric varactors, i.e., ferroelectrics, with the focus on thin film barium strontium titanate films.

## Chapter 3

# Ferroelectric materials and properties

#### 3.1 Introduction

This Chapter summarizes the most important aspects of ferroelectric materials, as an introduction to the studies on BST-based capacitors presented in the remainder of this thesis.

Ferroelectrics are a class of dielectrics with a spontaneous polarization, which can be reversed in an electric field [25]. Dielectric materials are insulators. In capacitors the dielectric layer is located in-between two electrodes. Unlike conventional dielectrics used in the integrated circuit technology, e.g.,  $SiO_2$ ,  $Si_3N_4$  or  $Al_2O_3$ , the relative permittivity  $\varepsilon_r$  of ferroelectric material is a nonlinear function of the electric field E.

An applied voltage results in an orientation of the polarization in the electric field E. The polarization P in ferroelectrics is remnant after the applied voltage is removed, is reversible, and saturates with increasing |E| [79]. The  $\varepsilon_{\rm r}$  of a capacitor can be obtained from non-hysteretic P(E) curves by calculating the susceptibility  $\chi$ , i.e., the slope of the curve at each measured E [79]. Successively, the  $\varepsilon_{\rm r}(E)$  can be computed by

$$\varepsilon_{\rm r}(E) = 1 + \chi(E) \tag{3.1}$$

at a constant operation temperature T.

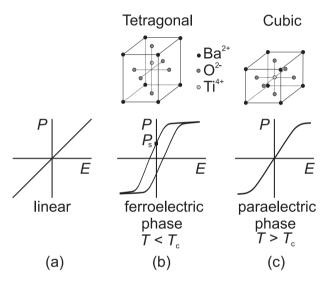

The P(E) curves of a linear capacitor, and that of a nonlinear ferroelectric capacitor in the ferroelectric and the paraelectric phases are depicted in Figure 3.1 with a brief summary of various properties of the two crystal phase structures given in Table 3.1. A single material can exhibit two crystal phase structures. In this dissertation the material will be named a ferroelectric capacitor, even if the temperature response is studied at in the paraelectric phase.

**Figure 3.1** – In (a) the P(E) response of a linear capacitor, in (b) a nonlinear capacitor in the ferroelectric phase (with hysteresis) and in (c) a nonlinear capacitor in the paralectric phase (without hysteresis).

| Ferroelectric phase                                                             | Paraelectric phase                                                                           |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| $T < T_{\rm c}$                                                                 | $T > T_{ m c}$                                                                               |

| non-centrosymmetric                                                             | centrosymmetric                                                                              |

| e.g., tetragonal crystal                                                        | cubic crystal                                                                                |

| hysteresis                                                                      | no hysteresis                                                                                |

| spontaneous polarization $P_{\rm s}$                                            | no $P_{\rm s}$                                                                               |

| typically higher $\varepsilon_{\rm r}$ , $\eta$ and $\tan \delta_{\varepsilon}$ | typically high $\varepsilon_{\mathrm{r}}$ , and lower $\eta$ and $\tan \delta_{\varepsilon}$ |

**Table 3.1** – The ferroelectric and paraelectric phase of a ferroelectric material.

A linear capacitor has a constant  $\varepsilon_r$ , since the slope remains unaltered (see Figure 3.1a and also a measurement example in Figure 5.14). The  $\varepsilon_r$  of a nonlinear capacitor reduces with increasing |E| due to the saturation of

the polarization (see, e.g., Figure 6.12). At the phase transition temperature of a nonlinear capacitor the crystal structure changes shape as depicted in Figure 3.1. The actual phase transition point, which affects the  $\varepsilon_{\rm r}$ , is modeled by the Curie-Weiss relation for small-signals at  $0\,V_{\rm dc}$  in the paraelectric phase

$$|\varepsilon_{\rm r}| = \frac{\varepsilon_0 C_{\rm curie}}{T - T_0}$$

(3.2)

with  $\varepsilon_0 = 8.85 \cdot 10^{-12} \,\mathrm{F/m}$  the permittivity of free space,  $C_{\mathrm{curie}}$  the Curie constant, and  $T_0$  the Curie-Weiss phase transition temperature.  $T_0$  is equal to or a few degrees Celsius less than the Curie temperature  $T_{\mathrm{c}}$  [34].

In the ferroelectric phase, the capacitor exhibits a non-centrosymmetric crystal structure. For BaTiO<sub>3</sub> at room temperature it is a tetragonal distorted lattice. Dipoles in adjacent unit cells align and form domains, which are separated by domain walls [79].

The polarization without applying an (external) electric field is called spontaneous polarization  $P_{\rm s}$  [79] and is due to a displacement of the ions from the cubic lattice positions (see Figure 3.1b). After the ferroelectric has been processed, the domains are randomly distributed and no residual polarization occurs [24].

Let's focus on a barium strontium titanate ferroelectric in the ferroelectric phase as an example (see the crystal structure in Figure 3.1). The titanium (Ti) is in the center of the octahedron, is shifted relative to the oxygen atoms in the ferroelectric phase and is relatively free to move in the octahedron [24]. When the Ti has moved from the center, a permanent dipole moment is formed, and the domains are formed in the ferroelectric [24].

A large external electric field changes the direction of the polarity and more domains will be aligned towards the direction of the electric field [24]. The ferroelectric phase induces a hysteretic P(E) behavior which is dominated by the movement of domain walls [25]. Hysteresis correlates with an increase in dielectric loss (see Section 3.3) and a steeper P(E) slope (compared to a capacitor in the paraelectric phase), which increases the  $\varepsilon_{\rm r}(0\,V_{\rm dc})$ , close to the coercive (switching) voltage, and hence  $C_{\rm max}$ . The coercive field is defined as the electric field which is required to switch from  $P_s$  to zero P [34]. On the other hand, the paraelectric phase exhibits a centrosymmetric cubic crystal structure (see Figure 3.1c) without theoretically any spontaneous polarization nor hysteresis, resulting in a lower dielectric loss and  $\varepsilon_{\rm r}$ .

When the polarization is fully saturated, the  $\varepsilon_{\rm r,min}$  will be similar in the ferroelectric and in the paraelectric phase, except for the  $\varepsilon_{\rm r,max}$ , and consequently the tuning ratio increases with a higher  $\varepsilon_{\rm r,max}$  in the ferroelectric phase (see equation 3.6).

Single crystalline and poly-crystalline barium strontium titanate Single crystalline ferroelectrics consist of a continuous lattice structure without any grain boundaries. The  $\varepsilon_{\rm r}$  as a function of temperature of bulk single crystalline shows a peak of the  $\varepsilon_{\rm r}$  at  $T_{\rm c}$  which is extremely high in single crystalline materials due to a perfect dipole alignment, e.g., an  $\varepsilon_{\rm r}$  of tens of thousands have been measured for SrTiO<sub>3</sub> [80]. Consequently, the P(E) curve is very steep, and narrow attributing to a highly temperature-sensitive  $\varepsilon_{\rm r}$  [81].

Poly-crystalline materials contain grain boundaries. The properties of poly-crystalline thin and thick films differ from those of single crystalline films [23, 25]. Typically, the transition between the ferroelectric and paraelectric phase is smeared out against the temperature due to local variations in stress, orientation, and additional defects such as grain boundaries [82–84], and compositional variations.

The single crystalline bulk value of  $Ba_{0.7}Sr_{0.3}TiO_3$  at 300 K can reach an  $\varepsilon_r = 5000$  [85]. The  $\varepsilon_r$  in thin poly-crystalline films is generally more than an order of magnitude lower (see Figure 6.17). Experimental results have shown that in thin films the relative permittivity  $\varepsilon_r$ , the tuning ratio  $\eta$ , and the phase transition temperature  $T_0$  are lower, and the phase transition temperature region becomes wider compared to bulk ceramics [83, 86, 87]. A positive side-effect in thin films is that the  $\varepsilon_r$  is much less sensitive to temperature and these are therefore preferred in RF applications. A lower maximum  $\varepsilon_r$  compared to bulk materials is not important at high frequencies where capacitance values are typically small. The tuning ratio of thin films can already be sufficient for low-voltage applications.

The difference in  $\varepsilon_r$  between bulk ceramic and thin films can possibly be attributed to:

- 1) finer grains in thin films [82–84],

- higher residual stress caused by thermal strain due to a difference in thermal expansion of the substrate and the ferroelectric during processing [83, 88, 89]. A CTE mismatch between the substrate and the

dielectric can lead to cracks, which form an electrical and mechanical reliability issue. For instance, crack can grow during thermal cycling and mechanical stress. The cracks are made visible by a microscopic inspection. To reduce the risk of cracks in the ferroelectric on silicon, the dielectric thickness should be sufficiently thin, and

3) a more pronounced influence of the low relative permittivity interface layer on the measured  $\varepsilon_{\rm r}$  of thin films [87,90]. The ferroelectric layer can in some cases be partly interfaced with an interface layer with a low relative permittivity, e.g., due to material diffusion through the electrodes. The effect of the passive interface layer on the device properties of a parallel plate capacitor near a single metal-ferroelectric interface is described in [23,91] as

$$\frac{A}{C} = \frac{h}{\varepsilon_0 \varepsilon_{\rm r}} = \frac{h_{\rm film}}{\varepsilon_0 \varepsilon_{\rm film}} + \frac{h_{\rm interface}}{\varepsilon_0 \varepsilon_{\rm interface}}$$

(3.3)

with  $\varepsilon_{\rm r}$  the measured relative permittivity, h the entire dielectric thickness,  $\varepsilon_{\rm r,film}$  the relative permittivity of the ferroelectric,  $h_{\rm film}$  the thickness of the ferroelectric film,  $\varepsilon_{\rm r,interface}$  the relative permittivity of the passive interface layer and  $h_{\rm interface}$  the thickness of the interface layer. The interface layer reduces the measured capacitance ( $\varepsilon_{\rm interface} \ll \varepsilon_{\rm film}$ ) and therefore  $\eta$ . Hence, a capacitor with a thicker dielectric layer is less affected by an interface layer with a relative low  $\varepsilon_{\rm interface}$  (see equation 3.3).

All three possible causes can contribute and depend on the deposition procedures.

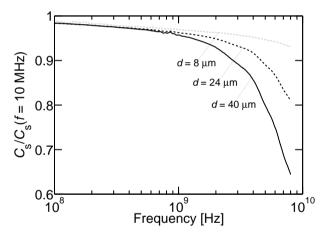

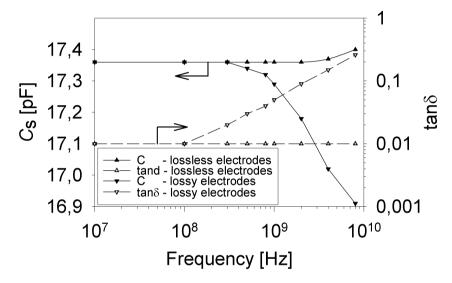

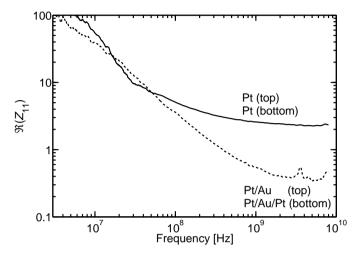

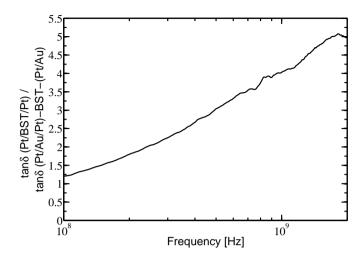

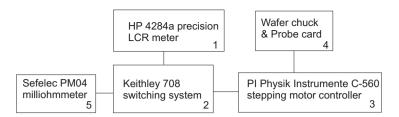

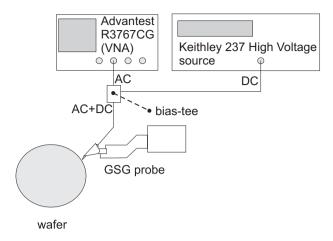

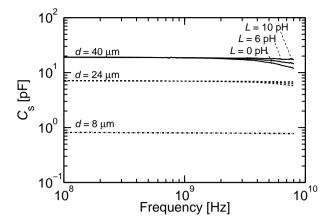

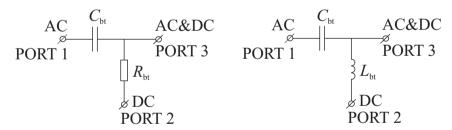

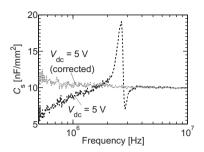

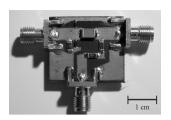

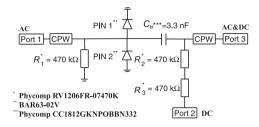

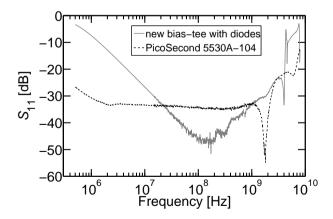

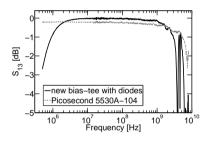

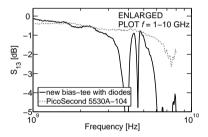

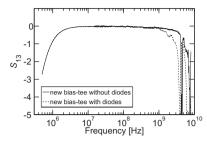

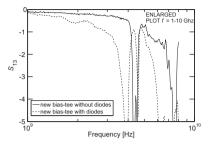

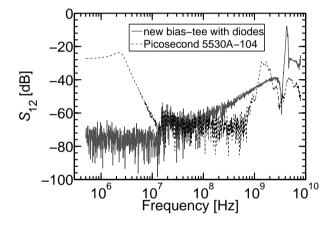

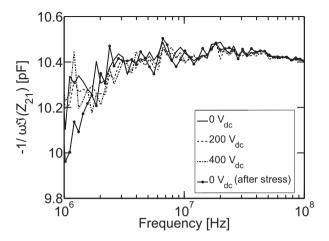

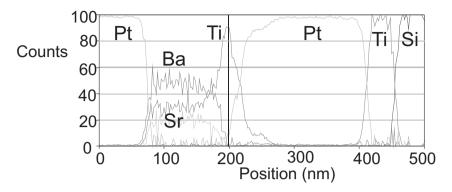

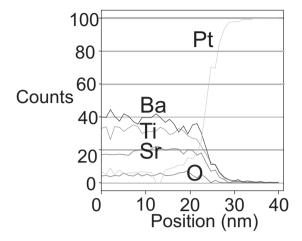

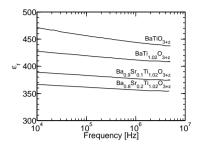

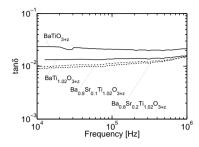

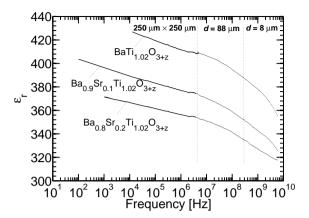

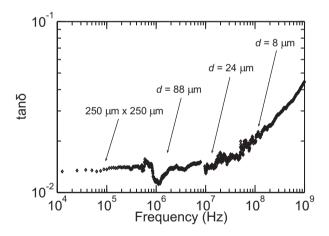

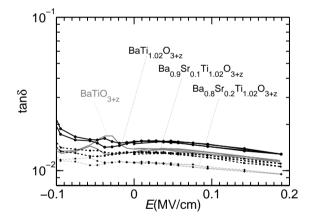

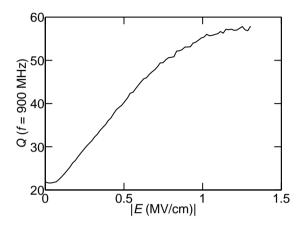

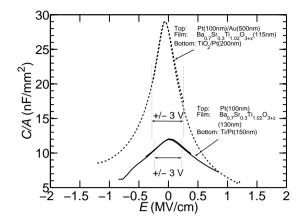

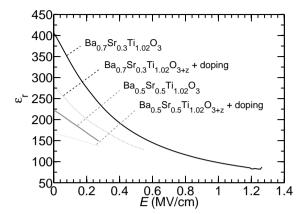

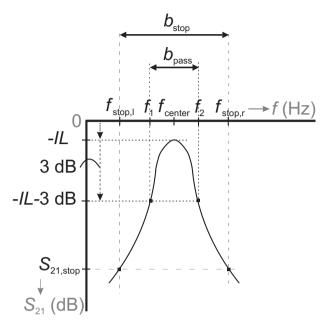

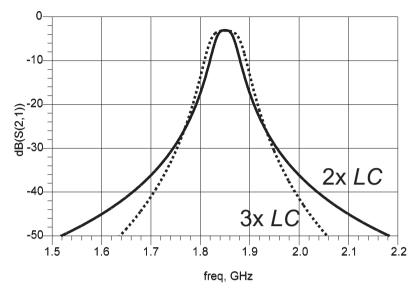

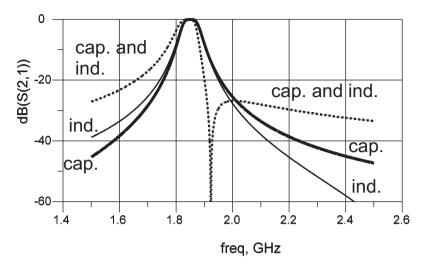

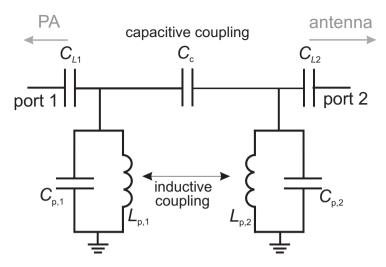

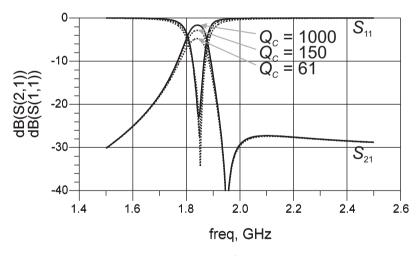

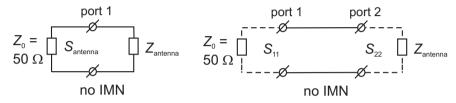

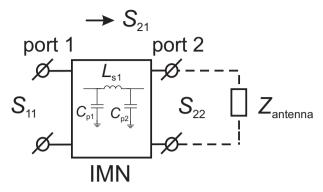

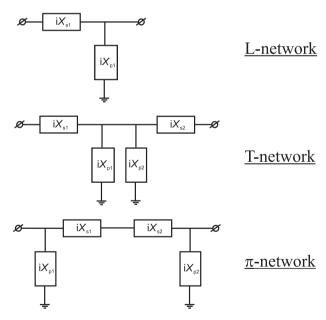

#### Frequency response